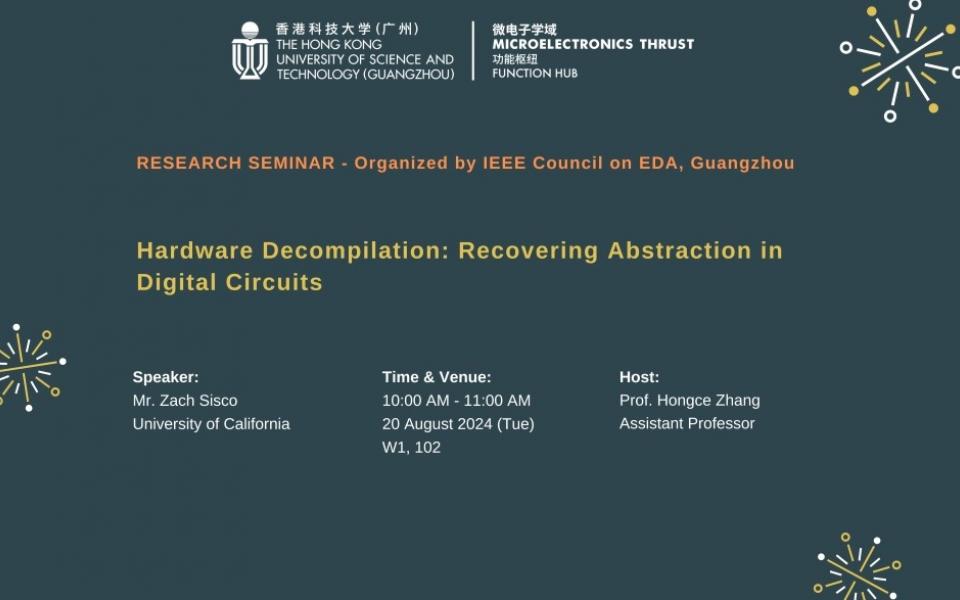

Public Research Seminar by Microelectronics Thrust, Function Hub, HKUST (GZ) - Hardware Decompilation: Recovering Abstraction in Digital Circuits

Supporting the below United Nations Sustainable Development Goals:支持以下聯合國可持續發展目標:支持以下联合国可持续发展目标:

Analyzing gate-level netlists is an essential part of the hardware development process: for functional simulation, behavioral verification, and logic equivalence checking. But these tasks are slow because netlists are large, low-level artifacts---further exacerbated by the inclusion of third-party IP. We can speed up these tasks by lifting gate-level netlists back up to high-level code in a hardware description language (HDL). My research opens this new area called "hardware decompilation". Through the use of solver-aided programming language techniques, hardware decompilation recovers higher-level programming abstractions in netlists and generates semantically equivalent HDL code.

In this talk, I will introduce what hardware decompilation is and the new design processes enabled by it. I will present a solution to one aspect of the problem called "hardware loop rerolling": identifying repeated logic in netlists and rerolling them into loops at the HDL level, significantly speeding up functional simulation. Then, I will give a preview of in-progress work addressing more aspects of hardware decompilation.

Zach Sisco is a PhD candidate at University of California, Santa Barbara. He is advised by Professors Jonathan Balkind and Ben Hardekopf. Zach's research is about applying solver-aided programming techniques to problems in hardware design. His website is: www.zsisco.net